2024-08-22

薄膜沉积是在半导体的主要衬底材料上镀一层膜。这层膜可以有各种各样的材料,比如绝缘化合物二氧化硅,半导体多晶硅、金属铜等。用来镀膜的这个设备就叫薄膜沉积设备。

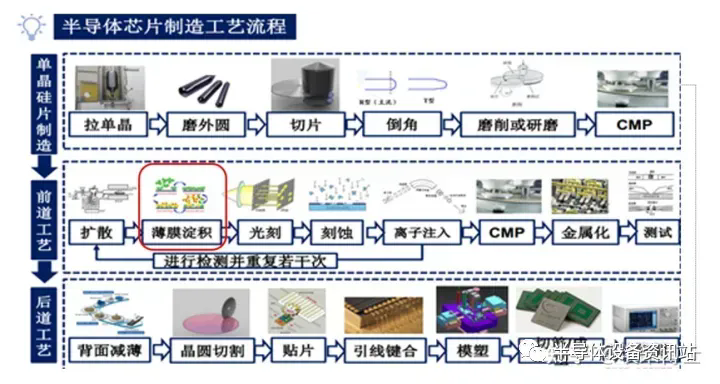

从半导体芯片制作工艺流程来说,位于前道工艺中。

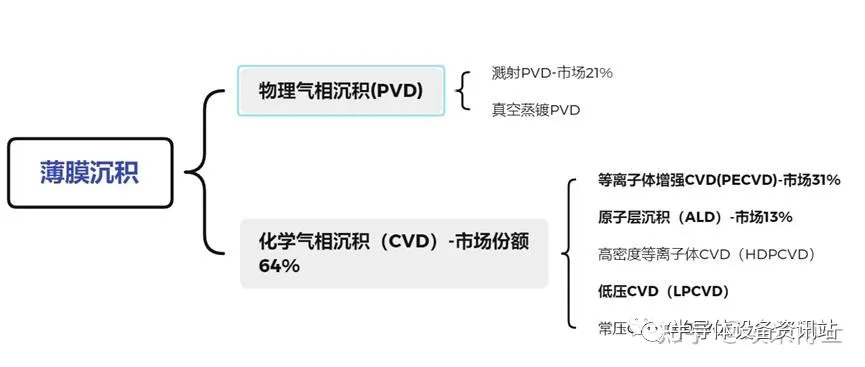

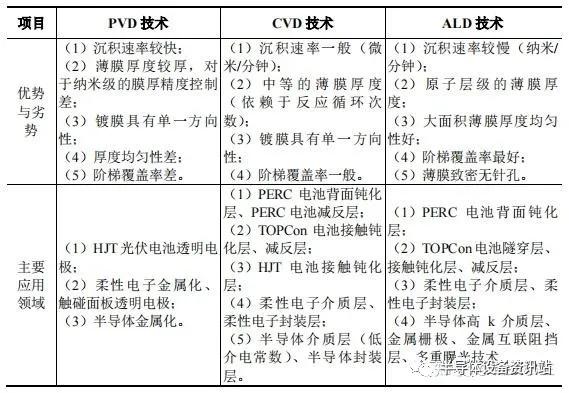

薄膜制备工艺按照其成膜方法可分为两大类:物理气相沉积(PVD)和化学气相沉积(CVD),其中CVD工艺设备占比更高。

物理气相沉积(PVD)指将材料源表面气化并通过低压气体/等离子体在基体表面沉积,包括蒸发、溅射、离子束等;

化学气相沉积(CVD)是指通过气体混合的化学反应在硅片表面沉积一层固体膜的工艺,根据反应条件(压强、前驱体)的不同又分为常压CVD(APCVD)、低压CVD(LPCVD)、等离子体增强CVD(PECVD)、高密度等离子体CVD(HDPCVD)和原子层沉积(ALD)。

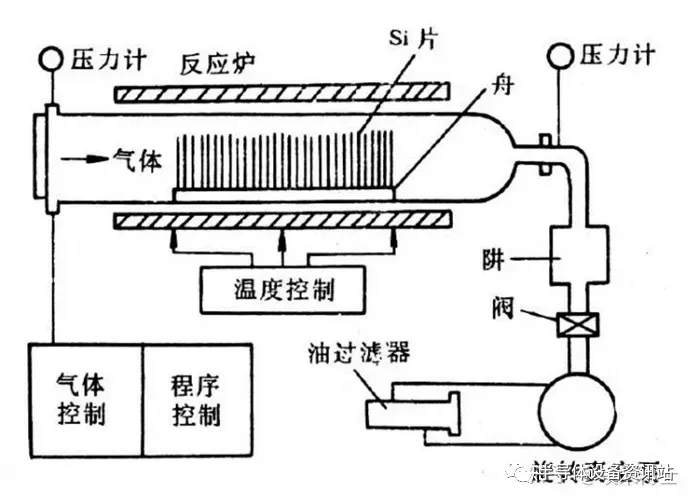

LPCVD:LPCVD具备较佳的阶梯覆盖能力,很好的组成成份和结构控制、很高的沉积速率及输出量、大大降低了颗粒污染源。依靠加热设备作为热源来维持反应的进行,温度控制、气压很重要。广泛运用于TopCon电池的Poly层制造。

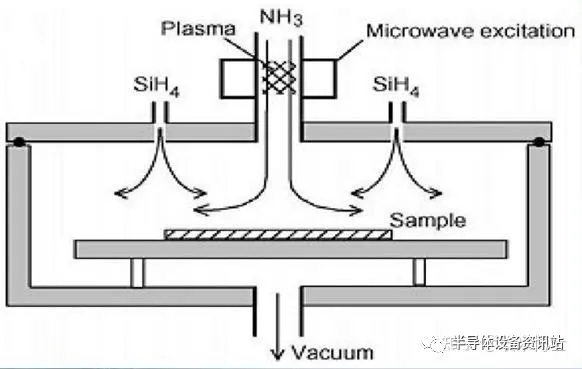

PECVD:PECVD依靠射频感应产生的等离子体,实现薄膜沉积工艺的低温化(小于450度)低温沉积是其主要优点,从而节省能源、降低成本、提高产能、减少了高温导致的硅片中少子寿命衰减,可应用于PERC、TOPCON、HJT等多种电池片的工艺中。

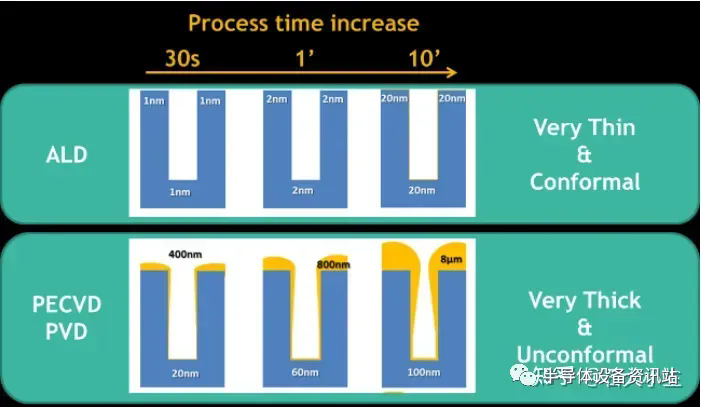

ALD:成膜均匀性好、致密无孔洞、台阶覆盖特性好、可在低温进行(室温—400℃)、可简单精确控制薄膜厚度、广泛适用于不同形状的基底、无需控制反应物流量均匀性。但缺点是成膜速度较慢。如用于生产纳米结构的绝缘体(Al2O3/TiO2)和薄膜电致发光显示器(TFEL)的硫化锌(ZnS)发光层。

原子层沉积技术(Atomic Layer Deposition,简称ALD)是一种将物质以单原子层形式逐层在基底表面形成薄膜的真空镀膜工艺。早在1974年,芬兰材料物理学家Tuomo Suntola开发了这项技术,并获得百万欧元千禧技术奖。ALD技术最初用于平板电致发光显示器,但并未得到广泛应用。直到21世纪初,ALD技术开始被半导体行业采用,通过制造超薄高介质材料取代传统氧化硅,成功解决了场效应晶体管因线宽缩小而引起的漏电流难题,促使摩尔定律进一步向更小线宽发展。Tuomo Suntola博士曾表示,ALD可显著增加组件的集成密度。

公开资料显示,ALD技术于1974年由芬兰PICOSUN公司Tuomo Suntola博士发明,在国外已经形成产业化,比如英特尔公司研发的45/32纳米芯片中的高介电薄膜。国内方面,我国引入ALD技术晚于国外三十多年。2010年10月,由芬兰PICOSUN公司和复旦大学主办了国内第一届ALD学术交流会,首次将ALD技术引入国内。

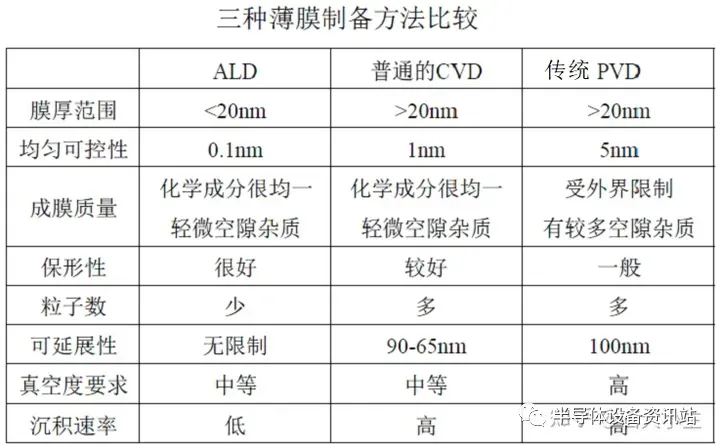

相比传统的化学气相沉积(Chemical Vapor Deposition,简称CVD)和物理气相沉积(Physical Vapor Deposition,简称PVD),ALD的优势在于成膜具备优异的三维保形性、大面积成膜均匀性,以及精确的厚度控制等,适用于在复杂的形状表面和高深宽比结构中生长超薄薄膜。

数据来源:清华大学微纳加工平台

在后摩尔时代,晶圆制造的复杂度和工序量大大提升。以逻辑芯片为例,随着45nm以下制程的产线数量增多,尤其是28nm及以下工艺的产线,对镀膜厚度和精度控制的要求更高,在引入多重曝光技术后,ALD需求工序数和设备数均大幅提高;在存储芯片领域,主流制造工艺已由2D NAND发展为3D NAND结构,内部层数不断增高,元器件逐步呈现高密度、高深宽比结构,ALD的重要作用开始凸显。从半导体未来的发展来看, ALD 技术将在后摩尔时代扮演着愈发重要的角色。

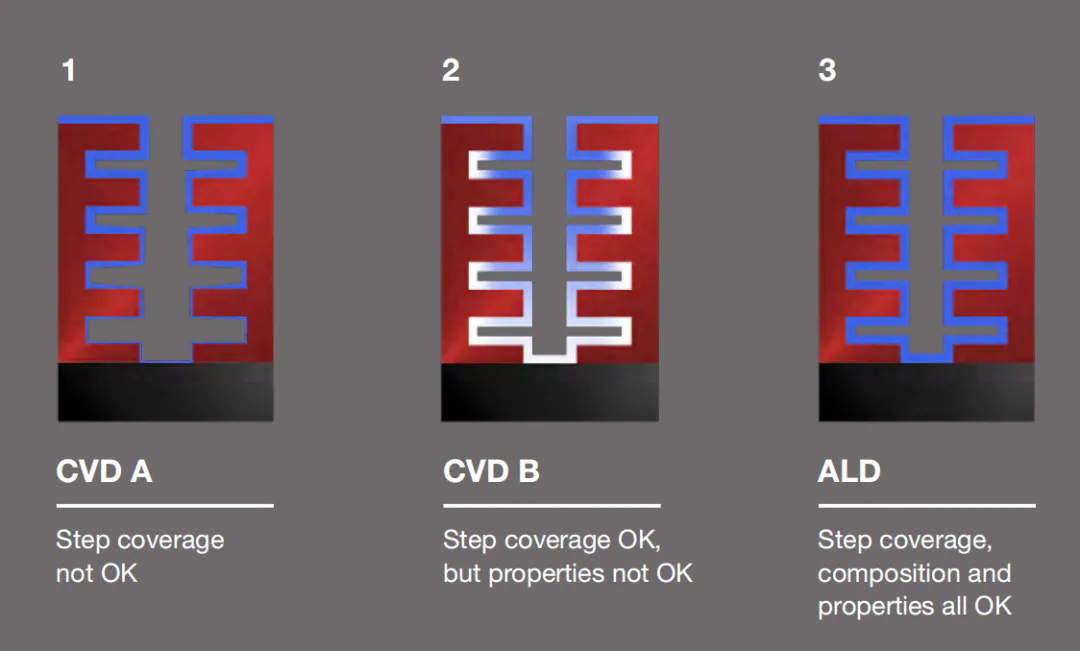

举例来看,ALD是唯一能够满足复杂3D堆叠结构(如3D-NAND)覆盖和薄膜性能要求的沉积技术。这从下图中可以很形象地看出,图中CVD A中沉积的薄膜(蓝色)并没有完全覆盖结构的下部部分;即使对CVD进行一些工艺调整(CVD B)实现了覆盖,但是底部区域的薄膜性能和化学成分很差(图中白色区域);相比之下,使用ALD技术则显示了完全的薄膜覆盖,而且在结构的所有区域都实现了高质量和均匀的薄膜特性。

相比CVD,ALD技术的优势(图源:ASM)

虽然短期来看,CVD依旧占据最大的市场份额,但是ALD已成为晶圆厂设备市场中增长最快的部分之一。在这个充满增长潜力且在芯片制造中扮演关键角色的ALD市场中,ASM公司是ALD设备领域的龙头企业。

扫一扫,在手机端打开当前页